1. Jurnal [Kembali]

2. Hardware [Kembali]

4. Prinsip Kerja [Kembali]

5. Video [Kembali]

6. Analisa [Kembali]

1. Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

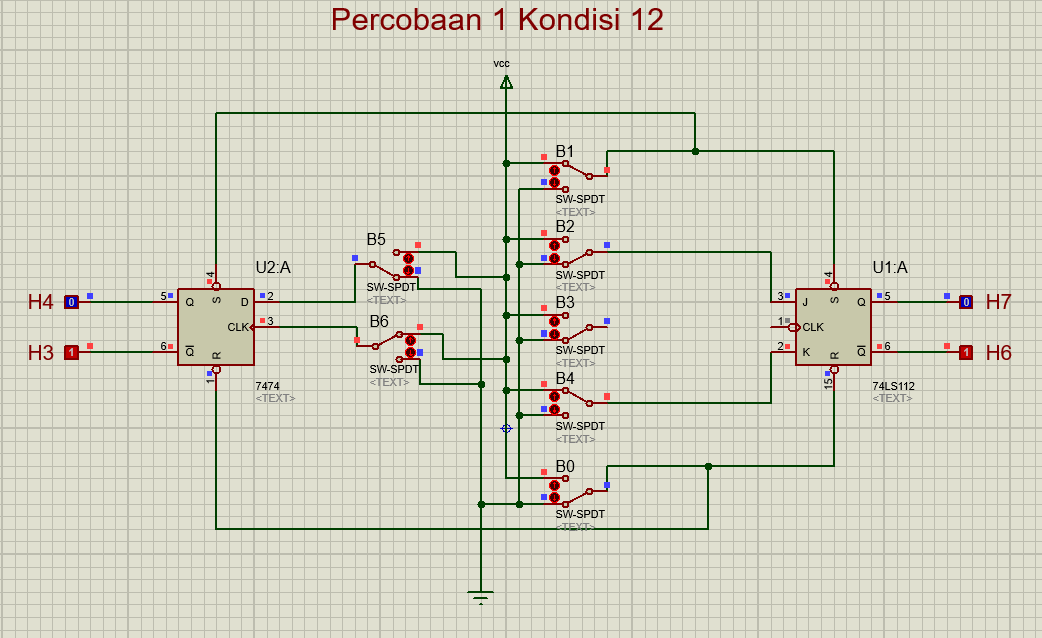

Jika pada B0 dan B1 diberi logika 0, maka iput yang terhubung dengan B0 dan B1 akan berlogika 0, dimana pada rangkaian yaitu pada input R (B0) dan S (B1). Dimana keadaan R dan S yang berlogika 0 menandakan bahwa input dalam keadaan aktif low, sehingga jika input pada R dan S dalam keadaan aktif maka untuk output hanya akan dipengaruhi oleh input pada R dan S, sedangkan untuk input dari J dan K serta clock tidak berpengaruh.

Maka untuk output yang diperoleh jika R dan S bernilai 0 adalah Q = 1 dan Q' = 1. Dimana kondisi ini menandakan keadaan terlarang. Karena ini berada dalam keadaan terlarang maka jangan menggunakan input tersebut karena dapat merusak komponen.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jika pada rangkaian B3 diputuskan maka untuk nilai inputan pada J dan K tidak akan memberikan pengaruh kepada output yang dihasilkan. sehingga yang menajdi sumber untuk output hanya dari R dan S saja. Dimana B3 yang terhubung ke clock pada JK Flip Flop merupa jantung bagi JK Flip Flop itu sendiri, jika tidak ada arus yang terhubung maka J dan K tidak akan berfungsi.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

Kondisi toggle adalah kondisi dimana output yang dihasilkan berupa keadaan yang berlawanan dengan otput yang dihasilkan sebelumnya. Misalkan output yang dihasilkan bernilai Q=1 dan Q'=0 maka jika dilakukan input yang berupa 11 maka outputnya Q=0 dan Q'=1 dan jika dilakukan seklai lagi maka outputnya akan berlwanan lagi yaitu Q=0 dan Q'=1.

Kondisi not change atau tetap adalah kondisi dimana output yang dihasilkan sama nilainya dengan output sebelumnya. Misalkan output sebelumnya Q=1 dan Q'=0 maka output yang dihasilkan dari input yang berupa 00 yaitu Q=1 dan Q'=0 dimana sama dengan output sebelumnya.

Kondisi terlarang pada flip-flop merupakan kondisi yang dapat merusak komponen flip -flop itu sendiri, dimana kondisi ini ditandai denga output yang dihasilkan bernilai 11. Adapun kondisi ini dikatakan terlarang karena outpu antara Q dan Q' berupa komponen yang berlawan, sehingga jika Q=1 maka Q'=0 nah disaat Q=Q' menjadi sesuatu permasalahan yang dapat merusak dan sangat dihindari penggunaannya.

Tidak ada komentar:

Posting Komentar