1. Jurnal [Kembali]

2. Hardware

[Kembali]

2.1 Alat

a. Jumper

Gambar 1. Jumper

3. Rangkaian Percobaan

[Kembali]

4. Prinsip Kerja

[Kembali]

Pada percobaan 3a, dimana pada setiap input dari IC 74192 dan IC 74193 dihunbungkan pada sumber yang sama dari setiap inputannya sehingga terdapat 8 buah saklar SPDT yang digunakan. Kemudian setiap sumber akan divariasikan inputanya yang mana saklar yang terhubung ke D1, D2, D3, dan D4 dibuat dalam kondisi tetap yaitu logika 0, sedangkan untuk nilai inputan ke UP, DN, PL, dan MR akan divariasikan. Jika inputan pad PL tersebut dibuat dalam kondisi 0 maka output akan menyesuiakan dengan inputan pada D1, D2, D3, dan D4. Dimana LED hanya akan menyala disaat kondisi PL berlogika '1' ,UP '1', DN 'clock', dan dan MR '0' maka led akan menyala dalam kondisi counter down pada setiap IC. Selain itu LED juga akan menyala disaat kondisi PL belogika '1', UP 'clock', DN '1', dan MR '0' sehingga led akan menyala dalam kondisi counter up disetiap IC.

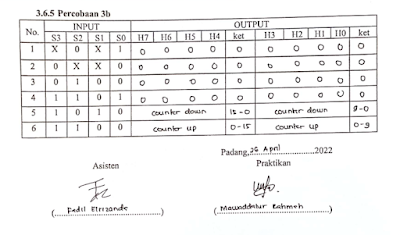

Pada percobaan 3b, dimana memiliki bentuk rangkaian yang sama seperti 3a namun ada pendambahan 2 buah gerbang OR yang dihubungkan ke inputan UP dan DN setiap IC. Jika inputan pada UP, DN, PL dan MR divariasikan maka inputan PL tersebut dibuat dalam kondisi 0 maka output akan menyesuiakan dengan inputan pada D1, D2, D3, D4. Adapun unutk membuat kondisi menyala maka PL harus berlogika '1' dan untuk UP dan DOWN dibuat dlam kondisi salah satu 1 dan satunya terhubung ke clock, dimana menjadikan salah satu terhubung ke clock maka saklar yang diberikan berlogika 0 karena terdapat gerbang logika OR yang akan mengubah kondisi ke clock. sehingga disaat PL berlogika 1, DN 0, UP 1 maka output yang dihasilakan berupa counter down, jika UP yang 0 maka counter up.

Adapun keadaan UP dan DOWN alah urutan bit yang ditampilkan oleh LED dimana UP dari 0000 ke 1111 (IC 74193) dan 0000 ke 1001 (IC 74192) sedangkan kondisi DOWN dari 1111 ke 0000 atau 1001 ke 0000.

6. Analisa [Kembali]

1. Analisa output percobaan berdasarkan IC yang digunakan

Pada IC 74193 akan dapat melakukan counter up dan down. Dimana untuk dapat menghasilkan berupa counter up maka input pada UP IC diberikan atau dihubungkan ke clock sedangkan untuk Down dihubungkan dengan logika '1' atau high, maka akan diperoleh output pada IC dalam kondisi up dari 0-15. Sedangkan untuk kondisi down maka dapat dilakukan dengan menghubungkan output Down be clock dan up '1' atau high, sehingga akan menghasilkan output dari 15-0 (down).

Pada IC 74192 juga dapat melakukan counter up dan down. Dengan prinsip kerja yang sama seperti lC 17493 dimana akan up disaat input up dihubungban ke clock dan input Down ke high. Sedangkan untuk counter down maka input up ke high dan down ke clock. Namun output yang dihasilkan saat up dari 0 sampai 9 dan saat down dari 9 ke 0.

2. Analisa hasil percobaan pada kondisi 3 dan 4

Pada Kondisi 3 dimana saat kaki input pada PL dan DN dihubungkan pada saklar yang berlogika 0 atau kondisi low maka output yong diperoleh. berdasarkan input pada D0, D1, D2 dan D3 pada IC.

Sedangkan untut kondisi dimana 4 input Load dan down dalam kondisi '1' atau high sedangkan input up diberikan ke clock mata output yang dihasilkan tidak bergantung ke inputan pada DO,D1, D2, dan D3.

Maka disaat input pada load bernilai 1 dan pada up atau down dihubungkan ke clock maka input load akan aktif sehingga output yang dihasilkan tidak akan bergantung ke input D0, D1, D2, D3.

3. Apa pengaruh gerbang OR pada rangkaian

Berdasarkan hasil percobaan dapat dilihat bahwa nilai OR akan mempengaruhi inputan pada pin up dan down pada IC yang akan mempengaruhi outputannya, sehingga output yang dikeluarkan disaat kondisi up terhubung ke clock dan down berlogika satu maka input yang diterima dari saklar pada up nya 0 (S1) dan pada down nyo 1 (12), sedangban pada kondisi down maka S1 berlogika 1 dan down 0 sehingga melewati gerbang or yang akan membalik keadaan input di Up akon berlogika 1 dan down akan terhubung ke clock sehingga output yang dihasilkan dalam keadaan down. Bahwa kondisi logika 0 dari saklar akan terhubung ke clock jika inputan dari gerbang or lain bernilai 1.

7. Link Download

[Kembali]

Tidak ada komentar:

Posting Komentar